While studying Udemy course “Digital Electronics & Logic Design Circuits” about 2’s complement and 1’s complement, I got puzzled with why all binary 1 (ex. 1111) is -1 in 2’complement, why positive 0 and negative 0 is same in 2’s complement, and why the range is different for 2’s and 1’s complements. I also had a misunderstanding that a negative number is the positive number with the most significant bit changed to 1, for example, -1 would be 1001.

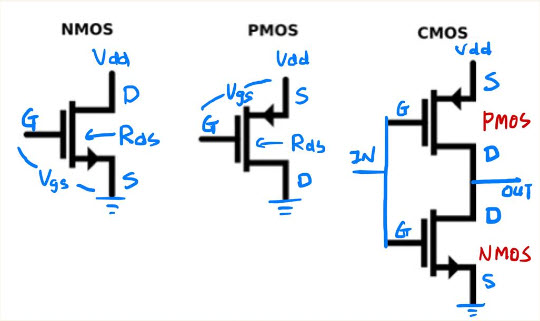

Later, I learned the purpose of the complement system is mainly to perform subtraction through addition, for instance 7 – 2 is the same as 7 + (-2). It becomes straightforward by first listing positive numbers, and then listing individual negative numbers for 1’s and 2’s complements. I drew the following table with N=4 as an example and everything became clear.

It answers my questions:

- Why 1111 is -1 in 2’s complement

- Why 2’s complement solves the double zero issue

- Why 1’s complement and 2’s complement have different ranges